Implementing an asymmetric multicore processor in Verilog requires designing diverse cores, enabling inter-core communication, and adding a scheduler for efficiency.

Asymmetric multicore processors (AMPs) are an advanced architecture allowing cores with different functionalities and performance levels to collaborate efficiently. Implementing an AMP in Verilog, a hardware description language (HDL), involves modeling and simulating the system before actual fabrication.

Verilog enables designers to create precise representations of each core, optimize their performance, and ensure seamless communication. This process allows for enhanced flexibility in handling complex tasks, making AMPs ideal for embedded systems where efficiency and performance need to be carefully balanced. This article will provide a detailed guide on AMP implementation using Verilog.

Introduction to Asymmetric Multicore Processors:

Asymmetric multicore processors differ from symmetric systems by integrating cores with varying capabilities. Unlike symmetric multicore processors (SMP), where all cores are identical, AMP features cores with different performance characteristics. This allows for efficient task management, optimizing resource allocation based on task demands.

For example, a high-performance core can handle compute-heavy operations, while a low-power core manages simpler tasks. This diversity in core functionality makes AMPs particularly beneficial for embedded systems, where energy efficiency and task prioritization are critical.

Designing an Asymmetric Multicore Processor Architecture:

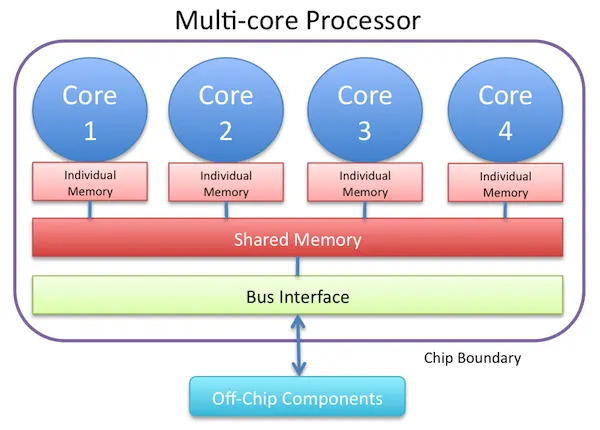

Designing an AMP system in Verilog begins with defining the architecture. The system includes multiple cores, a communication interface, and memory management. Cores can vary in complexity depending on their purpose. High-performance cores may have deep pipelines, while low-power cores are designed for efficiency.

A shared memory or interconnect system facilitates data exchange between cores. Additionally, a task manager allocates tasks to the appropriate core based on performance requirements. The architecture’s flexibility allows it to handle both high-priority and low-power tasks, optimizing for performance and energy conservation.

Defining the Core Modules in Verilog:

Each core in an asymmetric multicore processor is implemented as an individual module in Verilog. High-performance cores might require intricate designs with advanced instruction pipelines and floating-point arithmetic units, while low-power cores could be simpler with fewer stages.

The design process involves defining the instruction set, control unit, and memory hierarchy for each core. By assigning each core its unique functionality in Verilog, the system ensures the appropriate distribution of tasks based on core capabilities, balancing performance and energy efficiency in real-time processing environments.

Communication Between Cores:

In asymmetric multicore processors, communication between cores is critical for efficient data sharing and task management. A shared memory or interconnect system allows cores to exchange information seamlessly. This communication can be established using a bus or memory-mapped system where each core accesses shared resources.

Verilog’s flexibility enables the design of such inter-core communication architectures. The bus model, for example, connects multiple cores and facilitates data transfer. In a well-designed AMP, the communication system ensures synchronized data access, preventing conflicts and maximizing efficiency.

Task Scheduling and Core Allocation:

In asymmetric multicore systems, task scheduling plays a crucial role in assigning the right tasks to the appropriate cores. The task scheduler, implemented as a Verilog module, dynamically evaluates incoming tasks and allocates them to either high-performance or low-power cores.

By balancing tasks based on core capabilities, the system optimizes both speed and energy consumption. High-priority tasks are assigned to faster cores, while less demanding tasks run on energy-efficient cores. This task scheduler ensures efficient resource allocation, allowing the processor to handle multiple tasks simultaneously.

Steps for Implementing an Asymmetric Multicore Processor:

Design Core Modules:

Start by designing the cores, each tailored for its specific role. High-performance cores should support advanced instruction sets, while energy-efficient cores can be simpler. Customizing each core based on its function is crucial for achieving the desired balance between performance and power efficiency.

Use Verilog to define these cores with modular structures, making it easier to add or modify functionalities as needed. This flexibility in core design enables the system to handle a wide range of applications, from real-time processing to low-power tasks.

Establish Interconnects:

Design the communication system that allows the cores to share data and resources. This may include shared memory, bus systems, or custom interconnect architectures. The interconnect must ensure synchronized communication and prevent data conflicts. Efficient communication is critical for the performance of asymmetric multicore processors, especially when cores need to collaborate on tasks.

Verilog allows the designer to model complex interconnects, test them through simulations, and optimize for performance. A well-designed interconnect ensures smooth data flow and maximizes the processor’s efficiency.

Implement Task Scheduling:

The task scheduler manages which core will execute each task. In Verilog, this is implemented as a control module that dynamically allocates tasks to the appropriate core. Effective scheduling ensures that tasks are completed quickly and efficiently, balancing the workload across different cores.

The scheduler should take into account core performance, energy consumption, and task priorities. By optimizing task allocation, the asymmetric multicore processor can achieve higher throughput and better energy efficiency, making it suitable for a wide range of embedded applications.

Simulate and Optimize the System:

Simulate the entire system in Verilog using tools like ModelSim or Vivado. This helps to identify any issues in the core designs, interconnects, or scheduling algorithms. During simulation, test the system under various workloads to ensure it functions correctly and efficiently.

Optimization involves refining the design to improve performance, reduce power consumption, or increase core utilization. By continuously testing and optimizing, you can ensure that the asymmetric multicore processor meets the desired specifications and performs well in real-world applications.

FAQ’s:

1. What is an asymmetric multicore processor?

An asymmetric multicore processor integrates cores with varying performance levels to handle diverse tasks efficiently.

2. How are cores designed in Verilog for AMP systems?

Each core is designed as a separate Verilog module, customized for performance or energy efficiency based on its task requirements.

3. Why is communication important between cores in AMP systems?

Effective communication ensures smooth data exchange between cores, preventing conflicts and optimizing task performance.

4. What is the role of a task scheduler in AMP?

The task scheduler dynamically allocates tasks to appropriate cores based on priority, optimizing both performance and energy consumption.

5. What tools can be used to simulate AMP systems in Verilog?

Tools like ModelSim or Vivado are used to simulate and optimize AMP systems in Verilog.

Conclusion:

Designing and implementing an asymmetric multicore processor in Verilog provides a flexible, powerful solution for handling complex tasks efficiently. By defining heterogeneous cores, establishing communication, and implementing dynamic task scheduling, you can optimize the system for performance and energy efficiency.